Matthew Nutt

Electrical & Computer Engineering Senior at Rice University

About

Welcome to my website! I am a 4th-year undergraduate at Rice University pursuing a Master’s in Electrical & Computer Engineering, with a specialization in silicon engineering and computer architecture. My long-term goal is to help design the next generation of computing technology.

Outside of classes, I enjoy weightlifting, composing music, and learning new cooking recipes.

Projects

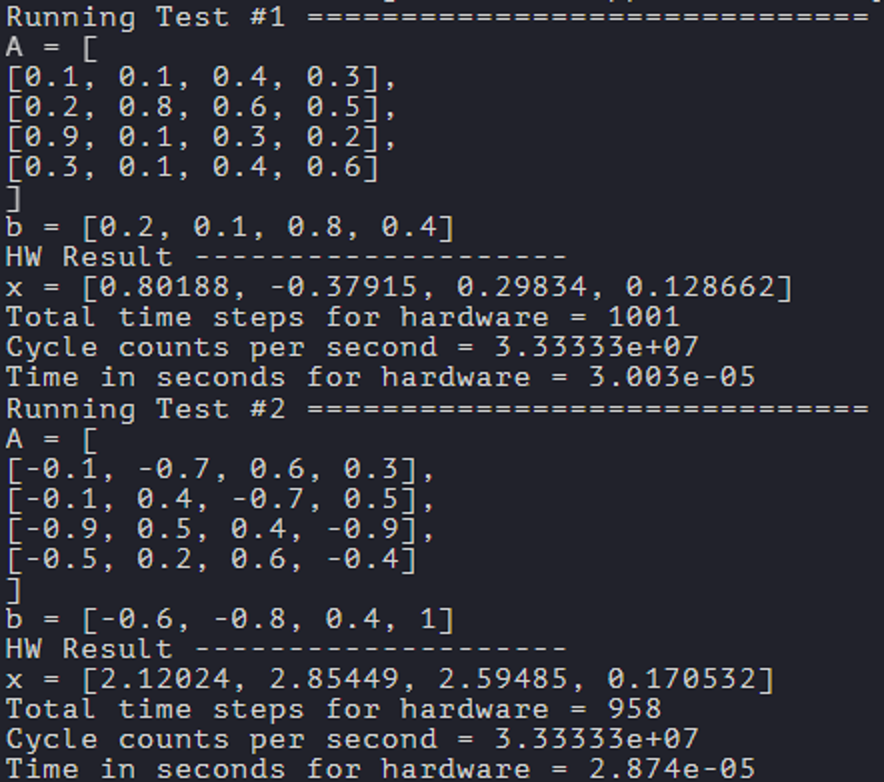

FPGA Linear System Solver December 2025

Linear systems can be solved via the QR decomposition (QRD) of the system matrix, which can be calculated with the resource-friendly CORDIC algorithm. This project is an implementation of a QRD-based solver algorithm for 4x4 matrices written in C++, synthesized via Vitis HLS and AMD Vivado, and tested on an AUP-ZU3 FPGA development board. The implementation achieved 29.5µs latency with an average deviation of 0.097% from expected results.

View Report PDF

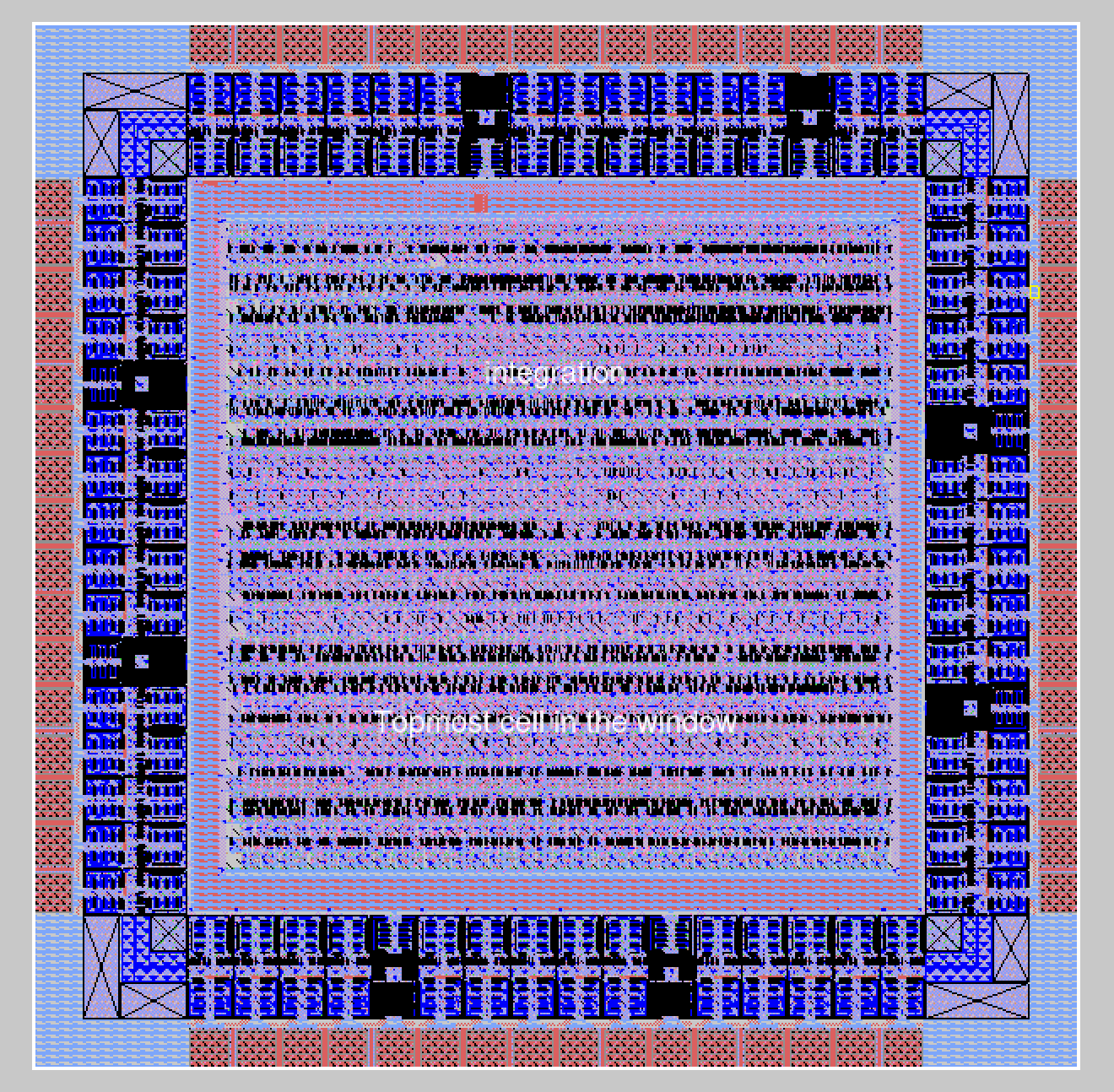

Snake Game ASIC May 2025

This project is an ASIC that plays a basic version of the snake game, featuring an 8x8 multiplexed display grid, randomly generated “food” positions, and dual-phase clocking. The system was implemented in Verilog, verified with testbenches on each module, synthesized, placed/routed, and then finally connected to a padframe to prepare for tapeout on the AMI 0.5μm process.

View Report PDF

View Repository

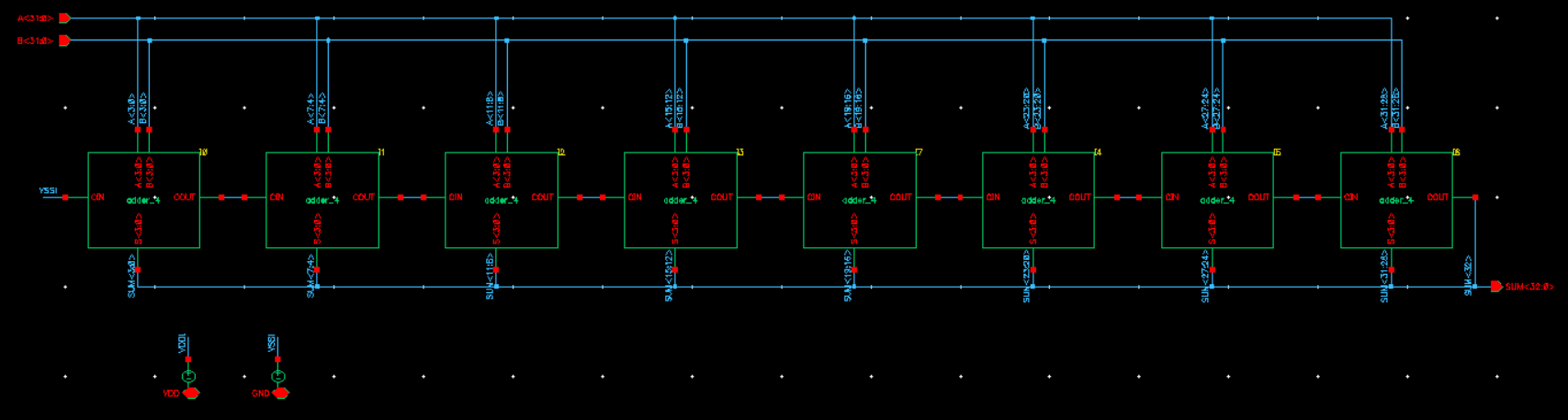

32-bit Carry-Bypass Adder April 2025

This is a schematic-level design of a 32-bit carry-bypass adder on the Skywater 130nm PDK, with eight bypass units and transistor/gate sizing optimization for each unit. Thanks to these optimizations, we achieved a critical path delay of 640ps with 133μW average power consumption.

View Report PDF

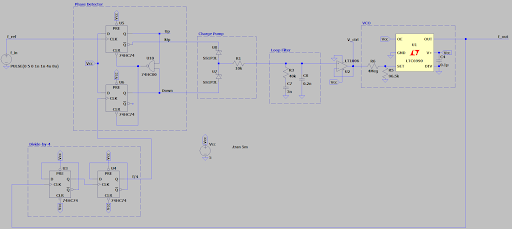

Power Supply Supervisor December 2024

For this project, my team designed a system that would monitor five power supply rails and generate a synchronous powergood output. The intention was that our design could be implemented into an ASIC with standard library cells. My main contribution was a 500KHz PLL that could achieve lock in 0.66ms and produced only 0.155% clock jitter.

View Report PDF

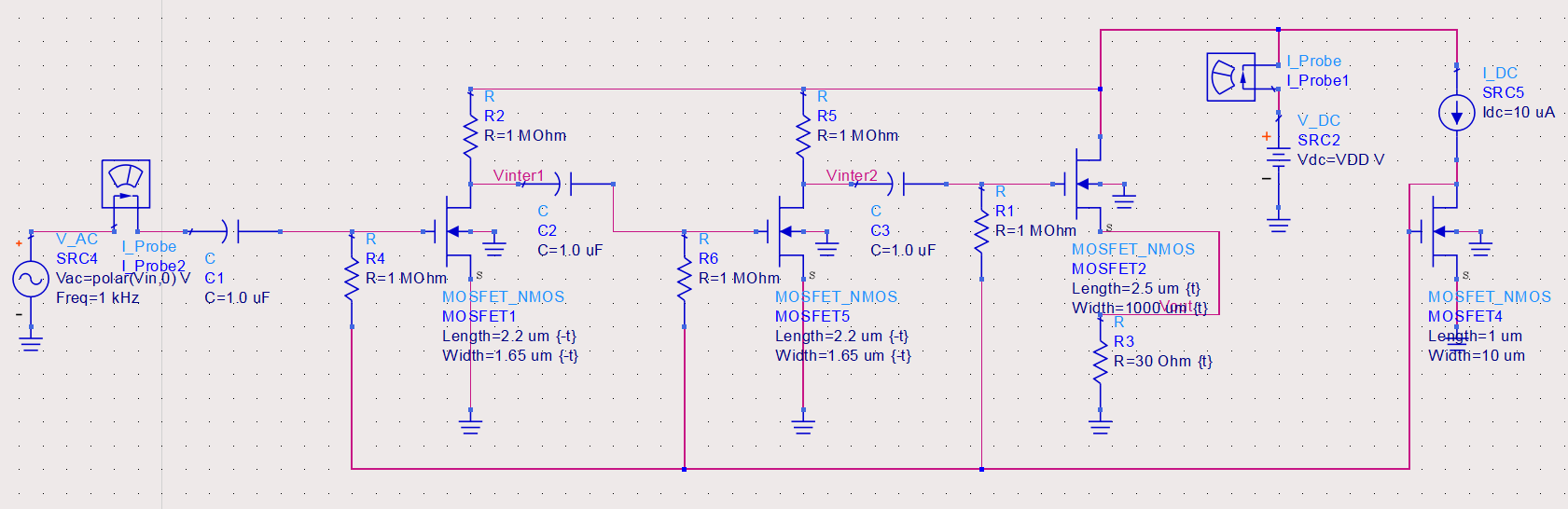

MOSFET Voltage Amplifier April 2024

This is a three-stage MOSFET voltage amplifier, designed and tested in Keysight ADS. Following optimizations, the amplifier achieved 20dB gain, 1.5MΩ input impedance, and 16Ω output impedance, all at a 0.75mW static power consumption.

View Report PDF

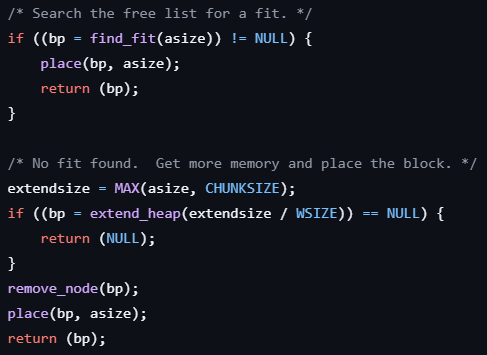

Dynamic Memory Allocator March 2024

As part of the Computer Engineering facet of my degree, I took a class that had us build a custom version of the malloc function in C. I programmed a segregated-list memory allocator with reallocation and coalescence, capable of 42 million operations per second with 68% average utilization.

Read More